Skew: LatchesQ1L112L2元1 12CombinationalLogic 1CombinationalLogic 2Q2 Q3D1 D2 D3sequencing overhead1 2 hold nonoverlap skewborrow setup nonoverlap skew2,2pd c pdqcd cd ccqct T tt t t t t tTt t t t2-Phase Latchessetup skewsequencing overheadhold skewborrow setup skewmax ,pd c pdq pcq pwcd pw ccqpwt T t t t t tt t t t tt t t tPulsed Latches 3:59 AM 10PRESENTED BY Sarbjeet Singh 11.

#Clock power on time borrowing flop full

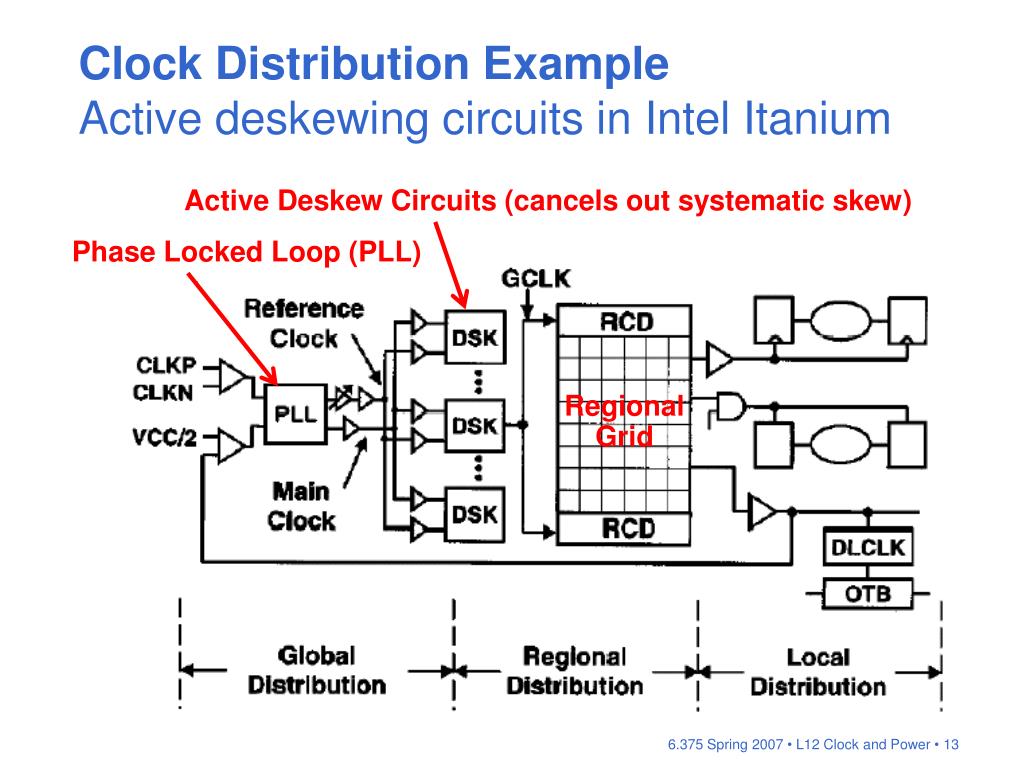

Review: Skew ImpactF1F2clkclk clkCombinational LogicTcQ1 D2Q1D2tskewCLQ1D2F1clkQ1F2clkD2clktskewtsetuptpcqtpdqtcdtholdtccqsetup skewsequencing overheadhold skewpd c pcqcd ccqt T t t tt t t t Ideally full cycle isavailable for work Skew adds sequencingoverhead Increases hold time too 3:59 AM 9PRESENTED BY Sarbjeet Singh 10. Clock SkewWe have assumed zero clock skewClocks really have uncertainty in arrival timeo Decreases maximum propagation delayo Increases minimum contamination delayo Decreases time borrowing 3:59 AM 8PRESENTED BY Sarbjeet Singh 9. Clock Skew: Spatial Clock VariationClock SkewDifference in clockarrival time at twospatially distinctpointsABABSkewCompressed timingpath 3:59 AM 7PRESENTED BY Sarbjeet Singh 8. Clock DistributionClockCannot really distributeclock instantaneouslywith a perfectly regularperiod 3:59 AM 6PRESENTED BY Sarbjeet Singh 7. How Much Borrowing?Q1L112L21 2Combinational Logic 1Q2D1 D2D2TcTc/2Nominal Half-Cycle 1 Delaytborrowtnonoverlaptsetupborrow setup nonoverlap2cTt t t2-Phase Latchesborrow setuppwt t tPulsed Latches 3:59 AM 5PRESENTED BY Sarbjeet Singh 6. Time Borrowing ExampleLatchLatchLatchCombinational LogicCombinationalLogicBorrowing time acrosshalf-cycle boundaryBorrowing time acrosspipeline stage boundary(a)(b)LatchLatchCombinational LogicCombinationalLogicLoops may borrow time internally but must complete within the cycle121 112 3:59 AM 4PRESENTED BY Sarbjeet Singh 5. Time Borrowing In a flop-based system:Data launches on one rising edgeMust setup before next rising edgeIf it arrives late, system failsIf it arrives early, time is wastedFlops have hard edges In a latch-based systemData can pass through latch while transparentLong cycle of logic can borrow time into nextAs long as each loop completes in one cycle 3:59 AM 3PRESENTED BY Sarbjeet Singh 4.

ObjectiveTime BorrowingClock SkewIEEE PAPERResultsConclusions 3:59 AM 2Sarbjeet Singh 3. 616NITTTR CHD 3:59 AM 1PRESENTED BY Sarbjeet SinghĢ. 1.SUBMITTED BY:-Sarbjeet SinghECE Regular 2011Roll No.

0 kommentar(er)

0 kommentar(er)